# The Design of A 125W L-Band GaN Power Amplifier

This paper describes the design and evaluation of a single stage 125W L-Band GaN Power Amplifier using a low-cost packaged transistor. The amplifier is optimized for the 0.96 to 1.215 GHz band with a typical band center gain of 20dB and output power at P-3dB of +51dBm (125W) at a PAE (for the connectorised amplifier) of > 70%. The design is based on a commercially available discrete 0.25µm GaN transistor, housed in a metalbased ceramic package (the QPD1008 from Qorvo). The amplifier uses 32mil thick Rogers 4360G2 PCB material mounted on an aluminium carrier.

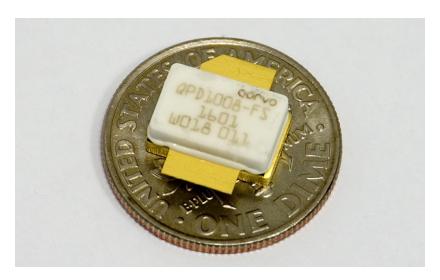

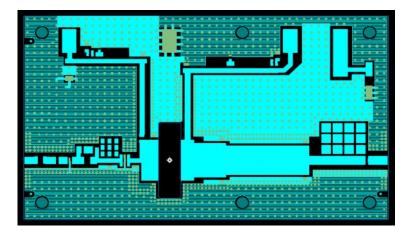

QPD1008 (NI360 Packaged) GaN Transistor

### Introduction

The range and performance of commercially available Gallium Nitride (GaN) discrete transistors is steadily increasing and the parts now available from leading manufacturers have impressive RF performance in terms of their available gain, RF output power and efficiency. For RF output powers in the order of tens of watts SMT packages can be considered. For higher output power levels metal based ceramic packages can be used. This greatly improves the thermal performance, as the source of the device is directly connected to the heatsink. This paper demonstrates that excellent performance can be realized at L-band from such a packaged part, namely the QPD1008 from Qorvo pictured above. The QPD1008 is a 0.25µm GaN device housed in an industry standard NI360 package (photograph shows the non-flange mount version).

## Design

The transistor is mounted on an aluminium carrier machined so the package tabs interface to the selected PCB material; 32mil thick Rogers 4360G2 with 1oz final metallization

weight. The relatively thick substrate was chosen to allow wide track widths of the required characteristic impedances to handle the high RF power levels and the DC current under large signal drive. The quiescent bias for the transistor is +50V with a drain-source current of 260mA.

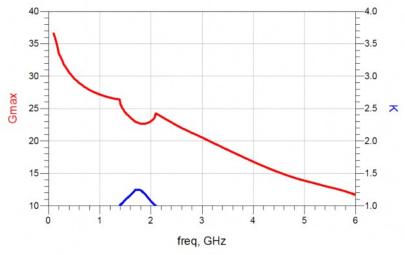

A plot of the transistor's measured Gmax (maximum available gain) is shown overpage. Breakpoints occur at 1.4GHz and 2.1GHz indicating a region of unconditional stability between these two frequencies. The operating band of the amplifier is in a region of conditional stability with a maximum stable gain of 26dB. The final amplifier gain will obviously be less than this due to the need for an amplifier that is unconditionally stable, the real losses associated with adding the matching and bias networks and the fact that the amplifier will be matched for power and efficiency rather than conjugately matched.

The amplifier needs to be unconditionally stable at all frequencies at operating temperatures down to -

**Transistor Gmax and Stability Factor**

40°C. Although the stand-alone transistor is unconditionally stable at around 1.8GHz, at frequencies above and below this it is potentially unstable, so steps must be taken to ensure stability in these regions. At low frequencies there is a very significant amount of available gain and it is essential that steps are taken to adequately suppress this.

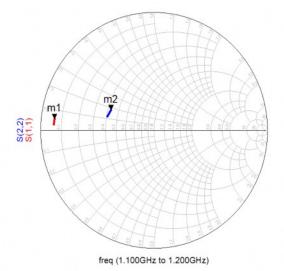

Large signal load pull data for the mounted device demonstrated that at 1.1GHz the device is capable of delivering around +51dBm output power at 3dB compression. The target load impedance at the output reference plane was found to be  $5\Omega + j2\Omega$  and the target source impedance at the input reference plane was found to be  $0.73\Omega + i0.64\Omega$ . The Smith chart figure shows these impedances presented in an  $11.7\Omega$  characteristic impedance environment. Note that the target input impedance is very close to the short-circuit point on the Smith chart; it is also close to the edge of the stability circles. A degree of compromise is therefore required in the design process to ensure unconditional stability whilst simultaneously presenting a source impedance that provides good power transfer characteristics.

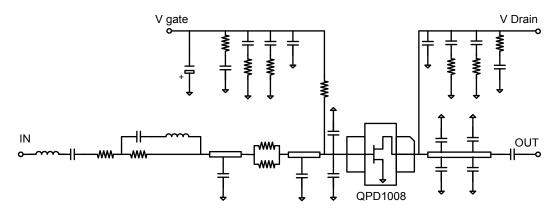

The amplifier schematic is shown overpage. All of the passive components (resistors and capacitors) are SMT parts and are carefully selected to handle both the required high DC voltages and high RF input powers. The capacitors are 800A series (250V) from ATC. The series RF resistors (required for ensuring unconditional stability) are mainly power resistors from IMS. These resistors can dissipate 25W of CW power in an 0805-size package. The bias networks for both the drain and gate make use of a printed transmission lines terminated

m1 freq=1.100GHz S(1,1)=0.883 / 173.695 impedance = 0.730 + j0.642 with a shunt SMT capacitor to provide a short circuit at mid-band. The transmission line is designed to present an open-circuit at the device and incur minimal RF loss. Additional RC decoupling is included at the gate and drain bias points to provide out-of band attenuation at low frequencies and ensure unconditional stability.

Input and output matching networks are low-pass structures that transform the  $50\Omega$  system impedance to the lower source and load impedances required for optimum power transfer.

m2 freq=1.100GHz S(2,2)=0.417 / 155.590 impedance = 4.996 + j2.086

**Desired Source and Load Impedances for maximum Power**

**PA Schematic**

The matching networks are implemented as mixed lumped/distributed structures with shunt SMT capacitors and printed series transmission lines. This is evident from the PCB layout plot shown below. It is essential that the transmission lines are wide enough to handle the expected RF power levels as if the tracks are too narrow they can simply vaporize under high RF drive.

An RF damping circuit was employed at the input of the amplifier which was a further measure to ensure low frequency stability and gain reduction. The circuit consists of a high value resistor by-passed in-band by a series LC resonator. The position and topology of the circuit was carefully chosen to provide maximum low frequency rejection with minimum impact on in-band performance. An important feature of the topology is that it avoids presenting any undesirable impedance to the device which could lead to oscillation.

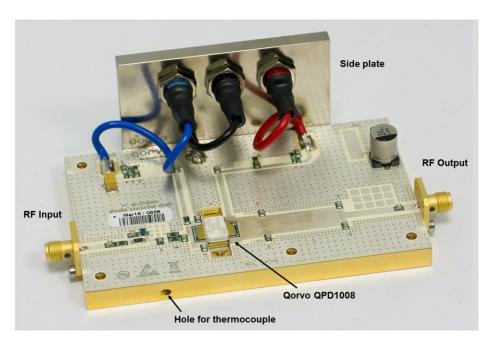

A photograph of the final assembled amplifier is shown overpage. The 32mil thick Rogers 4360G2 PCB is mounted onto an aluminum alloy carrier which acts as a heat spreader and can be fixed to a heat-sink.

A side-plate is fixed onto the side of the carrier through which bias is applied. The blue wire is for the gate bias, the red wire for the drain bias and the black wire is 0V. The RF input and output have been designed to mate with low-cost SMA connectors. Note the hole in the front face of the metal carrier. This allows a thermocouple to be placed underneath the packaged device to accurately measure the temperature at the base of the transistor.

# **Measured Performance**

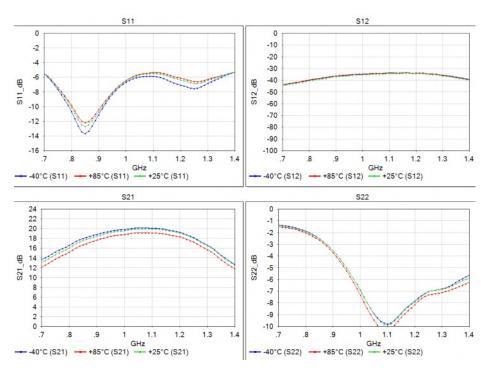

All of the measured results presented overpage are for the complete amplifier shown below, including connector losses. Small signal S-parameter measurements were carried out at package base temperatures of -40°C, +25°C and +85°C. These measurements were carried out CW; the results are shown in the plot overpage.

The S-parameter data demonstrates that the final amplifier has a small signal gain of around 19dB across the band which varies by less than 2dB over a wide temperature range. The input return loss is hardly affected by temperature and is 5dB worst case across the band. This relatively poor return loss is a function of matching to the desired source-pull impedance. The output return loss is nominally around 7dB. This is again a result of designing for a power match rather than a conjugate match.

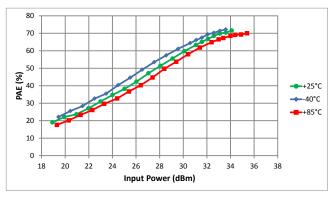

Large signal measurements were also carried out over temperature under pulsed conditions. The duty cycle was 10% and the pulse width was 128µs.

**PCB Layout**

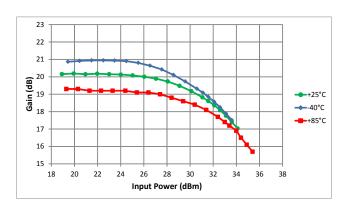

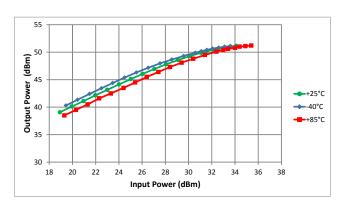

During the large signal measurements, the input power was swept from around 10dB back-off, up to and slightly beyond, 3dB gain compression. Over the power sweep, the dissipated power in the package increases so the package temperature increases. In the following results -40°C, +85°C and +25°C results are presented. The results were taken at mid-band (1.09GHz).

Gain variation with input power and temperature is shown in the plot overpage. From this it can be seen that 3dB gain compression is occurring at an input power of +33dBm at low temperature, +34dBm at nominal temperature and +35dBm at high temperature. The following plot of Pout versus Pin indicates that the mid-band output power at 3dB compression is nominally +51dBm, varying by just ±0.3dB over temperature.

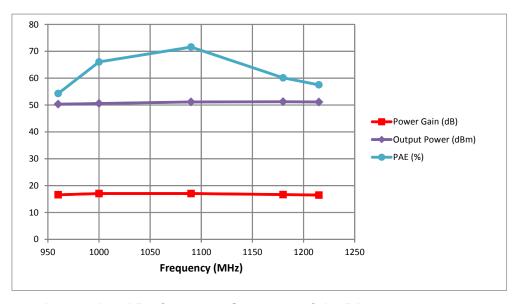

It can be seen in the third graph that Power Added Efficiency (PAE) is over 70% at all temperatures when the device is at the 3dB compression point.

Finally, the key performance metrics at 3dB compression are shown in the final plot at room temperature across the band of interest.

The PA achieves a minimum of 50dBm (100 W) output power, 54% PAE and 16.5 dB gain at P-3dB compression point at the band edges. At the centre of the band, efficiencies in excess of 70% are achieved. It is particularly noteworthy that these performance figures include losses associated with the matching networks and connectors. Similar performance has been replicated across a number of units.

### **Full Amplifier Assembly**

Measured S-parameters of the PA

## **Summary**

This paper has demonstrated that excellent wideband performance at L-band can be realized from a GaN transistor housed in a NI360 metal-based ceramic package such as the QPD1008 from Qorvo. A single stage power amplifier based on this device was designed for optimum performance from 960MHz to 1215MHz. At mid-band under nominal conditions, the amplifier has 20dB small signal gain, provides over +51dBm output power at 3dB compression (125W) with a corresponding PAE of 70%.

PAE versus Pin of the PA

Gain versus Pin of the PA

Pout versus Pin of the PA

Large-signal Performance Summary of the PA